BCD to 7-segment display decoder is a special decoder which can convert binary coded decimals into another form which can be easily displayed through a 7-segment display. BCD It is a digital numbering system in which we can represent each decimal number using 4 bits of binary numbers.

3 To 8 Decoder Vhdl

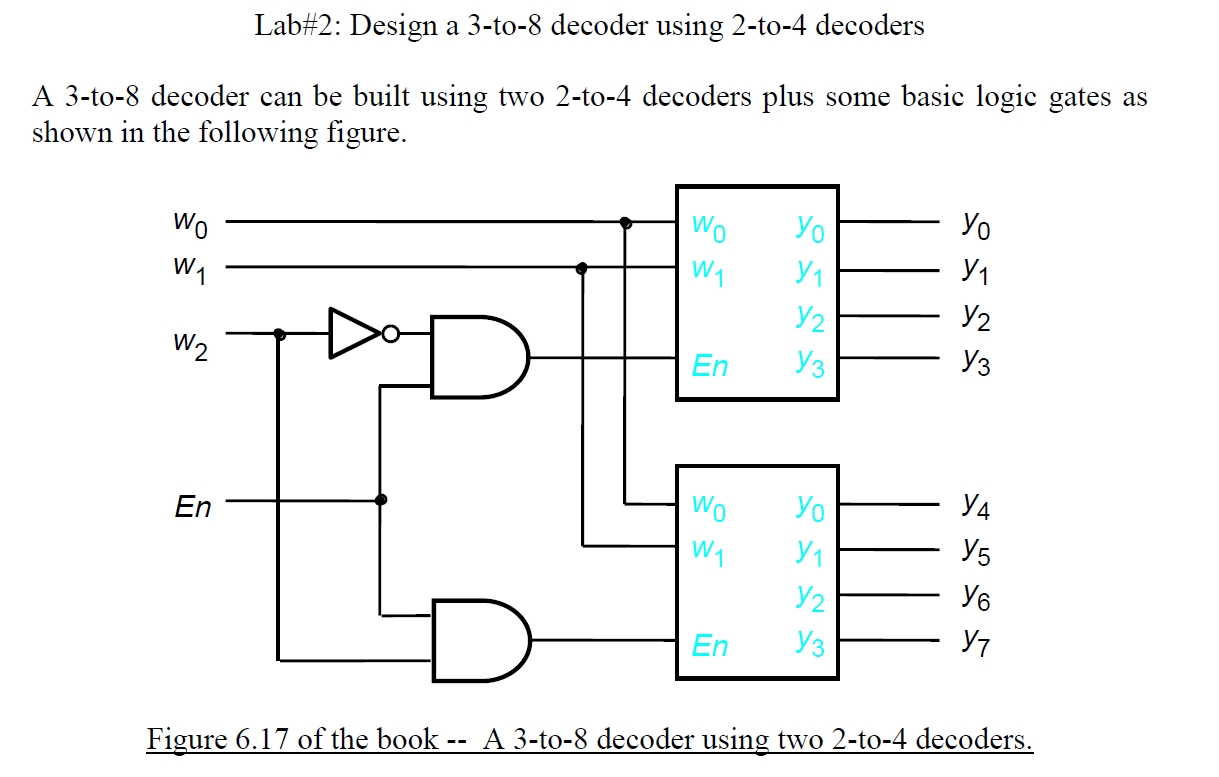

Decoder is one of the main combinational components in digital circuits. Decoders are mainly used in memory address decoding and data demultiplexing.

In this Verilog project, Verilog code for decoder is presented. The decoder is used for memory address decoding.

The 104 individual buttons or keys could be encoded into a standard ASCII code of only 7-bits (0 to 127 decimal) to represent each key or character of the keyboard and then input as a much smaller 7-bit B.C.D code directly to the computer. Keypad encoders such as the 74C923 20-key encoder are available to do just that. Positional Encoders. In this case, all decoder outputs will be 1’s except the one corresponding to the input code which will be 0. 2-to-4 line decoder with an enable input constructed with NAND gates. The circuit operates with complemented outputs and enables input E’, which is also complemented to match the outputs of the decoder NAND gate. VHDL code for 3x8 Decoder library ieee; use ieee.std Vhdl code 4x16 decoder using 3x8 decoder Search and download vhdl code 4x16 decoder using 3x8 decoder open source project / source codes from CodeForge.com. 0 Comments Leave a Reply. Write something about yourself. No need to be fancy, just an overview. Design of 2 to 4 Decoder using CASE Statements (Behavior Modeling Style)- Output Waveform: 2 to 4 Decoder VHDL Code.

Verilog code for 5 to 32 Decoder:

The decoder is implemented and successfully verified in the Verilog project of 32-bit MIPS processor here. The decoder is used in the register file for address decoding.

3. Verilog code for 16-bit single-cycle MIPS processor

4. Programmable Digital Delay Timer in Verilog HDL

5. Verilog code for basic logic components in digital circuits

6. Verilog code for 32-bit Unsigned Divider

7. Verilog code for Fixed-Point Matrix Multiplication

8. Plate License Recognition in Verilog HDL

9. Verilog code for Carry-Look-Ahead Multiplier

10. Verilog code for a Microcontroller

11. Verilog code for 4x4 Multiplier

12. Verilog code for Car Parking System

13. Image processing on FPGA using Verilog HDL

14. How to load a text file into FPGA using Verilog HDL

15. Verilog code for Traffic Light Controller

16. Verilog code for Alarm Clock on FPGA

17. Verilog code for comparator design

18. Verilog code for D Flip Flop

19. Verilog code for Full Adder

20. Verilog code for counter with testbench

21. Verilog code for 16-bit RISC Processor

22. Verilog code for button debouncing on FPGA

23. How to write Verilog Testbench for bidirectional/ inout ports

25. 32-bit 5-stage Pipelined MIPS Processor in Verilog (Part-1)

26. 32-bit 5-stage Pipelined MIPS Processor in Verilog (Part-2)

27. 32-bit 5-stage Pipelined MIPS Processor in Verilog (Part-3)

29. Verilog code for Multiplexers

29. Verilog code for Multiplexers30. N-bit Adder Design in Verilog

31. Verilog vs VHDL: Explain by Examples

32. Verilog code for Clock divider on FPGA

33. How to generate a clock enable signal in Verilog

34. Verilog code for PWM Generator

3x8 Decoder Vhdl Code Generator

35. Verilog coding vs Software Programming36. Verilog code for Moore FSM Sequence Detector